- 非IC关键词

供应GL850G-HHY50(SSOP28)Y50创惟GL850G-Y50/USB/GL850G-HHGXX系列

GL850G-HHY50

SSOP28

48个/管(9600个/包)

批次

周期

产品信息

深圳市华正源电子有限公司

型号:GL850G-HHY50

封装:SSOP-28

包装:48个/管 200管/真空包

年份:年份

可开16%税票

GL850G-HHY50是Genesys Logic先进的STT集线器解决方案,完全符合通用串行总线

规范修订版2.0。 GL850G-HHY50继承了Genesys Logic在成本和功耗方面的技术

高效的串行接口设计。 GL850G-HHY50具有经过验证的兼容性,低功耗和数字

比所有USB2.0集线器解决方案更好的成本结构。

GL850G-HHY50具有多种优势,可简化板级设计,有助于实现BOM(Bill

材料)系统集成商。 GL850G-HHY50集成了5V至3.3V和3.3V至1.8V的低压差

稳压器进入单芯片,因此无需外部LDO。

GL850G-HHY50嵌入了一个8位RISC处理器来操作控制/状态寄存器并响应

来自USB主机的请求。 GL850G-HHY50的固件将控制其通用I / O(GPIO)访问

外部EEPROM然后响应主机在外部配置的自定义PID和VID

EEPROM。内部掩码ROM中的默认设置在没有外部的情况下响应主机

EEPROM。 GL850G-HHY50为客户提供了更好的设计灵活性。复杂的设置,如PID,

VID,以及下游端口设置的数量......等。通过编程外部很容易实现

EEPROM或SMBUS模式(参考第5章)。

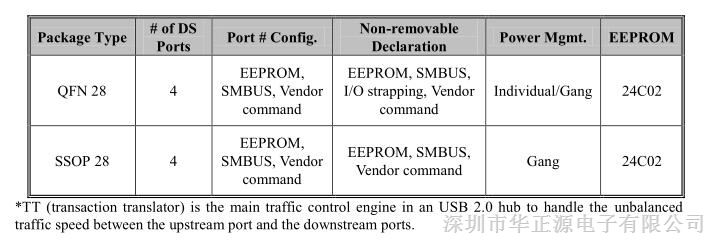

GL850G-HHY50是一款全功能解决方案,支持Individual和Gang(4个端口作为一组)模式

电源管理(单独模式仅适用于QFN28封装)。下游端口数量和

非/可移动下游端口可以通过不同方式配置,例如EEPROM,SMBUS,供应商

命令或I / O捆绑。有关详细配置方法,请参阅下表。

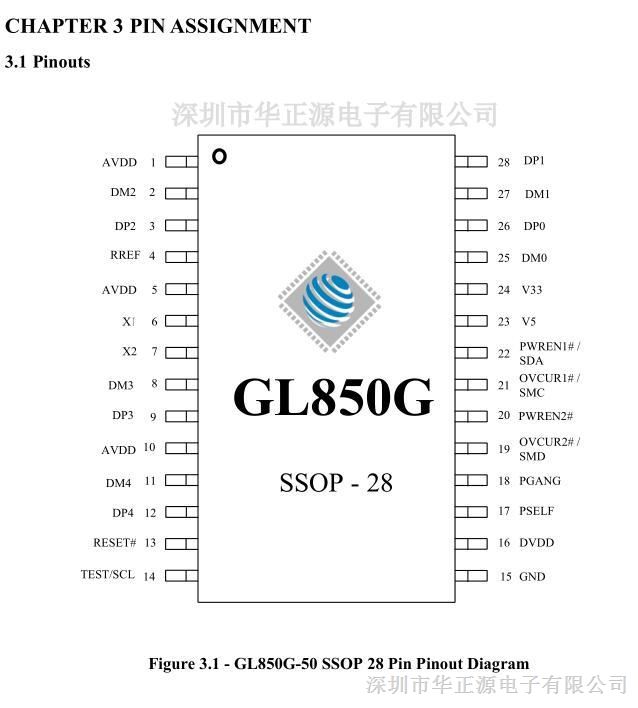

CHAPTER 2 FEATURES

---Compliant to USB Specification Revision 2.0

**Upstream port supports both high-speed (HS) and full-speed (FS) traffic

**Downstream ports support HS, FS, and low-speed (LS) traffic

**1 control pipe (endpoint 0, 64-byte data payload) and 1 interrupt pipe (endpoint 1, 1-byte data payload)

**Backward compatible to USB specification Revision 1.1

---On-chip 8-bit micro-processor

**RISC-like architecture

**USB optimized instruction set

**Performance: 6 MIPS @ 12MHz

**With 64-byte RAM and 4K mask ROM

**Support customized PID, VID by external EEPROM/ SMBUS/ Vendor command

**Support downstream port configuration by external EEPROM/ SMBUS/ Vendor command

---Single Transaction Translator (STT)

**Single TT shares the same TT control logics for all downstream port devices. This is the most cost

effective solution for TT.

---Integrate USB 2.0 transceiver

**Improve output drivers with slew-rate control for EMI reduction

**Internal power-fail detection for ESD recovery

---Low BOM cost

**Built-in 5V to 3.3V regulator

**Built-in upstream 1.5KΩ pull high and downstream 15KΩ pull-down

**Built-in PLL supports external 12 MHz crystal / Oscillator clock input

**Embed serial resister for USB signals

---Low power support

**Support Selective Suspend

**Support LPM L1 with EEPROM

---Smart power mode

**Support both individual and gang modes of power management and over-current detection for

downstream ports (Individual mode is not supported by SSOP 28 package)

**Conform to bus power requirements

---Flexible design

**Number of Downstream port can be configured by SMBUS / EEPROM/ Vendor command

**Compound-device (non-removable in downstream ports) could be configured by I/O strapping/

SMBUS / EEPROM/ Vendor command

**Automatic switching between self-p